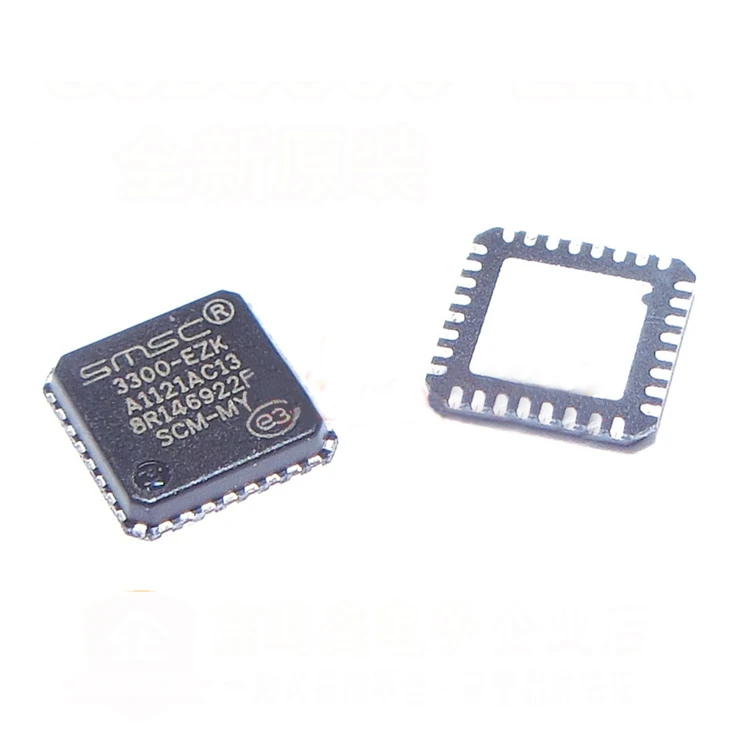

Usb3300 High Speed Usb Host Device Or Otg Phy 2.0 3.3v T/r 32-pin Qfn Ep Ic Chip Usb3300-ezk-tr - Buy Usb3300-ezk-tr,Usb3300,Usb3300 High Speed Usb Host Device Or Otg Phy 2.0 3.3v T/r

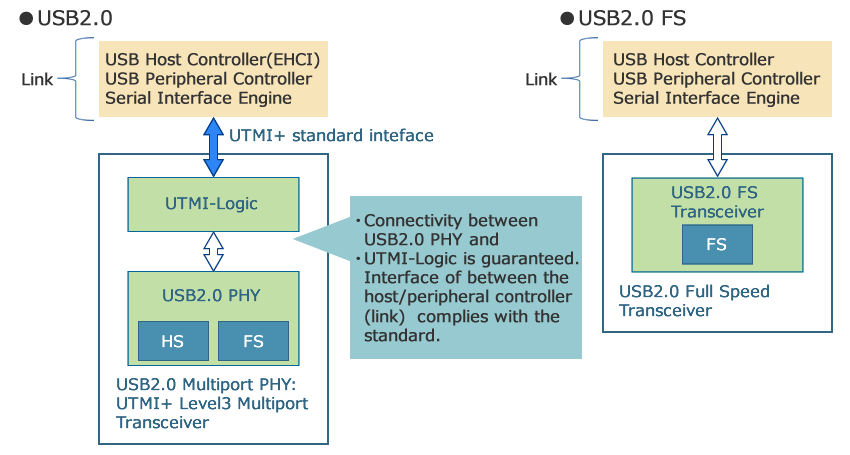

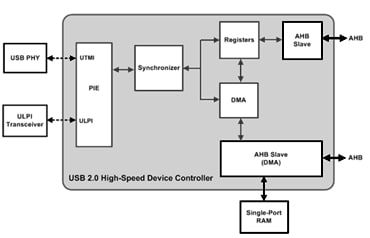

GOWIN Releases USB 2.0 PHY and Device Controller IP for Their FPGA Products | Civil + Structural Engineer magazine